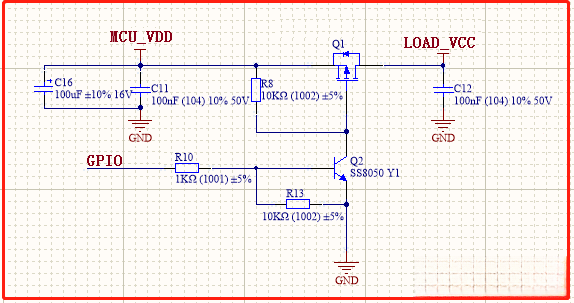

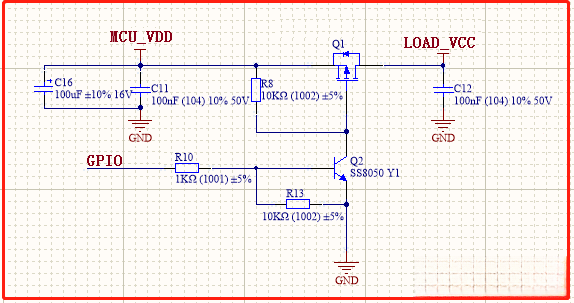

在低功耗系统中,为使整机功耗降到最低,外部的一些模块或电路会被单片机GPIO通过电子开关断电。

如上图所示,就是一个常用的电子开关模型,GPIO控制三极管Q2来拉高或拉低Q1场效应管的栅极电压。当GPIO设置为高时,Q2饱和导通,Q1的栅极拉低,Q1导通,被断电后外部LOAD电路得到MCU_VDD的供电。

当进入低功耗前,所有的电子开关都会关闭,即MCU通过GPIO控制,将所有耗电的外部电路、模块都断电,然后MCU自己也进入了低功耗模式;当从低功耗模式唤醒后,MCU会开启外部电路、模块,但是电子开关速度很快,如果外部电路、模块上本身带大电容,则在电子开关接通瞬间,大电容充电(相当于瞬间对地短路)产生极大电流,如附件图所示,Q1导通瞬间,由于LOAD电路中有大电容,MCU_VDD会在Q1导通瞬间因电流过大,电平被瞬间拉低然后回升。这样就产生了VDD的波动。

如何避免这种电源波动呢?

只需在R13电阻上并联一个电容即可,这样,当GPIO置高时,Q2基极的电压呈RC延时上升状态,Q2呈现的是缓慢导通的过程,所以Q1的导通也是缓慢的过程,LOAD电路中即使有大电容,也不会产生突然的超大电流影响MCU_VDD电平稳定性。

虽然每个工程师搭建的电子开关不一定完全一样,但基本原理和结构差不多。所以都可增加一个电容来解决电子开关快速导通导致的MCU_VDD电平突变问题。